International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified Vol. 5, Issue 7, July 2016

# High Performance Column Level ADC for **CMOS** Imager using Switched Capacitor Technique

## Anurag Yadav<sup>1</sup>, Rajesh Mehra<sup>2</sup>, Deep Sehgal<sup>3</sup>, H.S. Jatana<sup>4</sup>

ME Scholar, Department of Electronics and Communication Engineering, NITTTR, Chandigarh, India<sup>1</sup>

Associate Professor, Department of Electronics and Communication Engineering, NITTTR, Chandigarh, India<sup>2</sup>

Sci/Engr 'SF', VLSI Design Division, Semi-Conductor Laboratory, Mohali, India<sup>3</sup>

Sci/Engr 'SG', Design and Process Group, Semi-Conductor Laboratory, Mohali, India<sup>4</sup>

Abstract: An integrating type analog to digital converter is commonly used to achieve a high resolution. In this work 12-bit Dual slope ADC is developed which is an integrating type ADC. To integrate the input signal it requires one integrator made up of one resistance in feed forward path and one feedback capacitance with opamp circuit. Switched capacitor based integrator is alternative technique to realize the integrating function. In this design resistance in feed forward is replaced with two switches and one capacitor. This technique requires non overlapping clock. One of the advantages of this technique is area minimization. This technique is easily compatible with technology. This dual slope column level ADC minimizes the conversion time. Two stage opamp is designed which has gain of 78.22 dB. This column level dual slope ADC is implemented using 180nm standard CMOS technology.

Keywords: ADC, CIS, CMOS, OPAMP.

#### I. INTRODUCTION

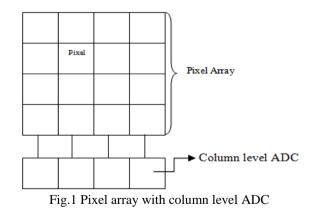

The requirement of CMOS image sensor is increasing day Power and surface area reduction is important since they by day. This is due to expansion in mobile imaging, video allow more number of channels on single chip. imaging camera, optical sensors and industrial machine vision. This situation is expected to continue with increasing demands from emerging applications in Smaller surface area and higher conversion rate are direct biomedical imaging, remote sensing, digital surveillance, sensor networks and robotics etc [1]. The column level ADC that has an ADC in each column due to this it can achieve a good trade off among silicon surface area, frame rate, power consumption and fill factor, therefore column level ADC is most widely used [2]. Very large scale integration is attracting much attention due to increasing need of miniaturization. Nano scale integration is demand of current scenario [3]. Today portable devices have main concern in VLSI. It is due to limited power supply through battery. So, circuit should consume less power [4]. In recent times many digital imagers like digital single lens reflex, camcorders, built in cameras have been developed. However with this development in digital cameras the demand of higher pixel resolution has increased [5]. The pixel size has become a main interest to achieve a high resolution [6]. In CMOS image sensor applications, it is difficult to integrate the complex calibration circuits in limited channel pitch [7]. The architecture of ADC should have less number of transistors and it should be less complex in size. The integrating type ADC is adopted due to its good linearity and uniformity. It occupies less surface area on a small column pitch [8]. Interconnection of pixel array and column level ADC is depicted in fig.1.

Technology scaling improves the digital performance.

benefits [9].

Surface area of the chip can also reduce with reducing the transistor's count [10]. Generally CIS comprises a pixel array, analog to digital converter and supporting digital blocks. Among them analog to digital converter converts the pixel voltage into digital code. Each pixel consists of one photodiode and some transistors. Photodiode is used to sense the light and transistor can act as reset, shutter and source follower [11]. Pixel converts light into electrical

#### International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 7, July 2016

signal. This electrical output goes to analog to digital converter, then a significant amount of digital processing image enhancement and compression occurs [12]. The architecture of pixel may change according to application. Depending upon the application of device the circuit will change [13]. The column level ADC have become popular because this have a large number of parallel ADC channels which provides high speed read out of large pixel arrays [14]. Popularity of these devices depends on small surface area, speed and reliability [15]. Scaling improves the transistor density on chip. It improves the frequency of operation and performance [16].

#### II. PROPOSED DUAL SLOPE ADC

Dual slope ADC is an integrating type ADC. It has high accuracy and linearity. So, it can be used as a column level ADC in CMOS image sensor. The dual slope ADC consists of integrator, comparator, counter and control logic. Generally integrator has one feed forward resistance and one feedback capacitance in RC technique. Resistance is depicted in equation 1.

$$R = \rho \frac{L}{A} (\Omega) \tag{1}$$

Where R = resistance,  $\rho$  = resistivity, A = a plane perpendicular to the direction of current flow, L = Length.

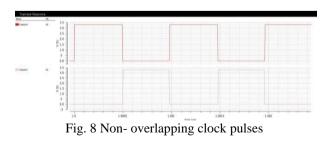

Switched capacitor technique is used in this design replace this resistance with two switches and one capacitor. This technique is helpful in area reduction. This technique provides accuracy in time constant and easily compatible with technology. Two non-overlapping clock pulses are required for the operation of integrator. When a clock has a value of 1 during that time other clock must have the value of 0. It means there is no overlapping between these two clock pulses. Capacitance which emulates resistance is found out with equation2.

$$R = \frac{T}{C}$$

(2)

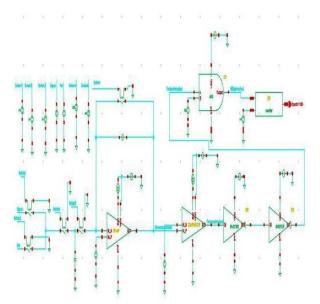

Where R= Resistance, C= capacitance, T= Time period of clock pulse. This technique is very useful in area reduction. Schematic of dual slope ADC is shown in fig.2.

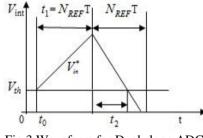

The conversion process of dual slope ADC is shown in fig.3.It is observed that the slope of the  $V_{int}$  is proportional to the amplitude of  $V_{in}^*$ . One reference voltage is given at the non inverting terminal of the integrator. Initially when switch1 is connected the integrator stabilizes itself at reference voltage. This reference voltage is provided at the non-inverting terminal of the integrator. At time  $t_0$  switch1 is disconnected. At this time switch2 connects integrator's inverting terminal to signal voltage  $V_{in}^*$ .

Fig.2 Full Schematic of Dual Slope ADC

Fig.3 Waveform for Dual slope ADC

At this time capacitor starts charging and counter starts counting to particular time  $t_1$ , and then reset the counter. The voltage  $V_{in}(t_1)$  at  $t = t_1$ .

$$V_{\text{int}}(t_{1}) = K \int_{0}^{N_{REF}T} V_{in}^{*} dt + V_{\text{int}}(0)$$

$$V_{\text{int}}(t_{1}) = K N_{REF} T V_{in}^{*} + V_{th}$$

(3)

Where  $t_1 = N_{REF}$  T and T = clock pulse.

At time  $t_1$  Switch3 is connected to reference voltage  $V_{REF}$ and capacitor starts discharging. Counter again starts counting. When the output of the integrator reaches to the threshold voltage  $V_{th}$  of comparator, the counter will be stopped and binary count can be converted in to digital word  $N_{out}$ .  $t_2$  is the time where the output of the integrator reaches to the  $V_{th}$  of comparator. The integrator voltage at  $t_1 + t_2$  is given as

$$V_{\text{int}}(t_1 + t_2) = V_{\text{int}}(t_1) + K \int_{t_1}^{N_{out}T + t_1} (-V_{REF}) dt = V_{th}$$

(4)

### International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 7, July 2016

Where  $t_2 = T + t_1$ Substituting Eq. 3 in Eq. 4.

$$\mathbf{K} N_{REF} \mathbf{T} V_{in}^* + V_{th} - \mathbf{K} V_{REF} N_{out} \mathbf{T} = V_{th}$$

(5)

solving Eq. 5 for  $N_{out}$

$$N_{out} = N_{REF} - \frac{V_{in}^*}{V_{REF}}$$

(6)

It has observed that  $N_{out}$  will be some fraction of  $N_{REF}$ , where fraction corresponds to the ratio of  $V_{in}^*$  to  $V_{REF}$  [17].

#### **III. TWO- STAGE OPERATIONAL AMPLIFIER**

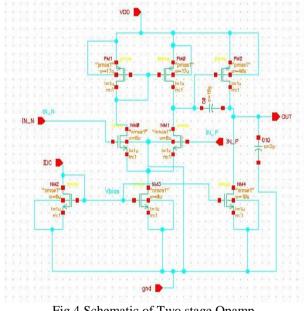

Differential amplifier can be considered as the single stage operational amplifier. The two stage opamp is the combination of differential amplifier and common source amplifier. The schematic of two stage opamp is depicted in fig.4

Fig.4 Schematic of Two stage Opamp

It is standard architecture with miller compensation technique applied in it. In two stage opamp first stage provides high gain and second stage provides large swings [18].

#### IV. RESULT AND DISCUSSIONS

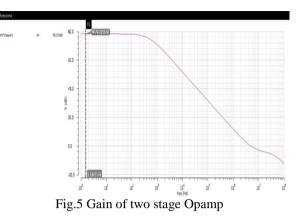

Two stage opamp is very important block for dual slope ADC. Gain of two stage ADC is observed from the simulation which is 78.22 dB and unity gain bandwidth is 5MHz. It can see in AC analysis. Simulation for gain is depicted in fig.5

The phase margin of opamp is shown in fig.6 .It is about  $44.81^{\circ}$ .

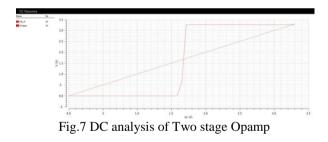

DC analysis of two stage opamp is depicted in the fig.7. Same opamp has been used as comparator with miller capacitor removed and addition of inverter stages at output.

It provides the value of input voltage where gain of opamp is high. Dual slope ADC using switched capacitor technique requires non overlapping clock pulses. The waveform of these pulses are shown in fig.8.

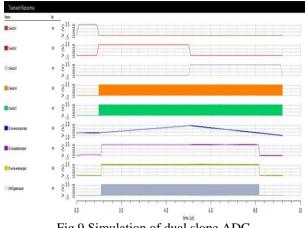

Simulation for proposed ADC is depicted in fig.9. It shows the operation of all the switches, non overlapping clock, conversion process, comparator output and AND gate output.

#### International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 7, July 2016

Fig.9 Simulation of dual slope ADC

Simulation of dual slope ADC shows the conversion time is  $9.2\mu s$ . Simulation of 12-bit counter is shown in figure 10.

When the integrator's output becomes equal to the threshold voltage of comparator counter stop counting and binary value converted in to digital form. The counter simulation is shown in the tabular form in table 1.

| TABLE1. Simulation of 12-bit counter | er |

|--------------------------------------|----|

|--------------------------------------|----|

| Analog<br>input | Reference<br>Voltage             | Threshold<br>voltage of<br>comparator | Dual slope<br>ADC<br>Output | Total<br>Steps   |

|-----------------|----------------------------------|---------------------------------------|-----------------------------|------------------|

| $V_{in}^*$      | $V_{\scriptscriptstyle R\!E\!F}$ | $V_{th}$                              | 12- bit                     | N <sub>out</sub> |

| in volt         | in volt                          | in volt                               |                             |                  |

| 1.65            | 2.4                              | 1.65                                  | 111111010100                | 4052             |

| 1.6             | 2.4                              | 1.65                                  | 111010010011                | 3731             |

| 1.55            | 2.4                              | 1.65                                  | 110101111111                | 3455             |

| 1.45 | 2.4 | 1.65 | 101101011000 | 2904 |

|------|-----|------|--------------|------|

| 1.35 | 2.4 | 1.65 | 100100110001 | 2353 |

| 1.25 | 2.4 | 1.65 | 011100001010 | 1802 |

| 1.15 | 2.4 | 1.65 | 010011100011 | 1251 |

| 1.1  | 2.4 | 1.65 | 001111010000 | 976  |

The problem in counter's count, it can be solve by compensation methodology. It will improve in future work. Design summary of dual slope ADC along with opamp parameters is presented in Table 2.

TABLE2. Design summary of Dual slope ADC

| Parameters                 | Proposed Work |  |

|----------------------------|---------------|--|

| Technology                 | 0.18 μm       |  |

| Type of ADC                | Dual slope    |  |

| Resolution                 | 12 bit        |  |

| Conversion time            | 9.2 μs        |  |

| Opamp used                 | Two Stage     |  |

| Gain of Opamp              | 78.22 dB      |  |

| Phase margin of Opamp      | 44.81°        |  |

| Opamp unity gain bandwidth | 5MHz          |  |

| Supply voltage             | 3.3 volt      |  |

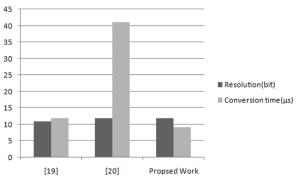

The comparison of this dual slope ADC with architecture of ADC implemented in previous work is depicted in table3.

TABLE3. Comparison of parameters with other ADC

| Parameters | [19]   | [20]    | Proposed<br>Work |

|------------|--------|---------|------------------|

| Technology | 0.18µm | 0.35 μm | 0.18 µm          |

| Type of    | SS/SAR | CDS-ADC | Dual             |

| ADC        |        |         | slope            |

| Resolution | 11 bit | 12 bit  | 12 bit           |

| Conversion | 12 µs  | 41 µs   | 9.2 μs           |

| time       |        |         |                  |

It shows reduction of 23.33% in conversion time ADC of [19] while resolution is increased by 1bit and When compared with [20] conversion time reduces to 77.56% keeping resolution of both ADC same at 12-bit. Graphical representation of comparison is shown in fig.11.

Fig.11 Graphical comparison of other ADC

International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 7, July 2016

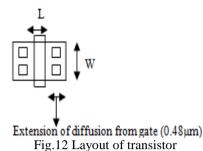

#### Tentative area prediction done for ADC:

Total area of transistor in fig.12 is  $(L+2\times0.48\mu m)\times W$ . Calculate the all transistor's area in this way of the circuit [7] and sum up all transistor's area of the circuit and then double the total area. This total area is the tentative area of that circuit. The total tentative area predicted of opamp is calculated from this way is 454.72  $\mu m^2$ . Layout density of standard cells in 180nm standard CMOS technology is 80Kgates  $/mm^2$ .61 cells are required for counter. The tentative area prediction done for ADC without counter is 943.64  $\mu m^2$ . The power consumption of whole ADC is 3.7271mW.

#### **V. CONCLUSION**

Dual slope ADC is an integrating type ADC and is suitable for column level ADC for CMOS imager due to its high linearity. This proposed ADC has been designed using switched capacitor technique along with non overlapping clock pulses. Simulation result of dual slope column level ADC using switched capacitor technique shows the reduction of 23.33% in conversion time when there is increase of 1bit in resolution and reduction of 77.56% in conversion time for same resolution over the work previously carried out as depicted in table 3. Simulation results also show the binary count of 12-bit counter. This proposed ADC has two stage opamp having gain of 78.22 dB with unity gain bandwidth of 5MHz.Simulation of ADC is carried out using an 180nm standard CMOS technology.

#### ACKNOWLEDGEMENT

I would like to thank Mr. Anil koul (scientist/ Engineer 'SD'), VLSI Design Division, Semi-Conductor Laboratory, Mohali, India for his support and valuable guidance.

#### REFERENCES

- [1] D. G. Chen, F. Tang, and A. Bermak, "A low-power pilot-DAC based column parallel 8b SAR ADC with forward error correction for CMOS image sensors," IEEE Transaction on Circuits System, Vol. 60, No. 10, pp. 2572–2583, October 2013.

- [2] Seunghyun Lim, Jeonghwan Lee, Dongsoo Kim and Gunhee Han, "A High-Speed CMOS Image Sensor With Column-Parallel Two-Step Single-Slope ADCs", IEEE Transactions on Electron Devices, Vol. 56, No. 3, pp. 393-398, March 2009.

- [3] Dinesh Sharma, Rajesh Mehra, "Low Power, Delay Optimized Buffer Design using 70nm CMOS Technology", International Journal of Computer Applications, Vol.22– No.3,pp. 13-18, May 2011.

- [4] Richa Singh and Rajesh Mehra, Power Efficient Design of Multiplexer using Adiabatic Logic, International Journal of Advances in Engineering & Technology, Vol.6, March 2013, 246-254.

- [5] Junan Lee, Himchan Park, Bongsub Song, Kiwoon Kim, Jaeha Eom, Kyunghoon Kim, and Jinwook Burm, "High Frame-Rate VGA CMOS Image Sensor Using Non-Memory Capacitor Two-Step Single-Slope ADCs", IEEE Transactions on Circuits and Systems, Vol. 62, No. 9, pp. 2147-2155, September 2015.

- [6] Seunghyun Lim, Jimin Cheon, Youngcheol Chae, Wunki Jung, Dong-Hun Lee, Minho Kwon, Kwisung Yoo, Seogheon Ham, and Gunhee Han, "A 240-frames/s 2.1-Mpixel CMOS Image Sensor with Column-Shared Cyclic ADCs", IEEE Journal of Solid-State Circuits, Vol. 46, No. 9, pp. 2073-2083, September 2011.

- [7] Min-Kyu Kim, Seong-Kwan Hong and Oh-Kyong Kwon, "A Small-Area and Energy-Efficient 12-bit SA-ADC With Residue Sampling and Digital Calibration for CMOS Image Sensors", IEEE Transactions on Circuits and Systems – II: Express Briefs, Vol. 62, No. 10, pp. 932-936, October 2015.

- [8] Yun-Rae Jo, Seong-Kwan Hong, Member, and Oh-Kyong Kwon, "A Low-Noise and Area-Efficient PWM- delta sigma ADC Using a Single-Slope Quantizer for CMOS Image Sensors", IEEE Transactions on Electron Devices, pp. 1-6, 2015.

- [9] Masato Yoshioka, Kiyoshi Ishikawa, Takeshi Takayama, Sanroku Tsukamoto, "A 10-b 50-MS/s 820-W SAR ADC With On-Chip Digital Calibration", IEEE Transactions on Biomedical Circuits and Systems, Vol. 4, No. 6, pp.410-416, December 2010.

- [10] Vandana Choudhary Rajesh Mehra, "2- Bit Comparator Using Different Logic Style of Full Adder", International Journal of Soft Computing and Engineering (IJSCE), Vol.3,Issue 2, pp. 277-279, May 2013.

- [11] Robert Johansson, A. Storm, C. Stephansen1, S. Eikedal1, T. Willassen1, S. Skaug, T. Martinussen, D. Whittlesea, G. Ali, J. Ladd, X. Li, S. Johnson, V. Rajasekaran3, Y. Lee, J. Bai, M. Flores, G. Davies, H. Samiy, A. Hanvey, D. Perks, "A 1/13-inch 30fps VGA SoC CMOS Image Sensor with Shared Reset and Transfer-Gate Pixel Control", IEEE Conference on International Solid-State Circuits, pp. 414-415, 2011.

- [12] S.Y. Soh, J. Jeong, A. Han, E. Kim, K. Hong, H. Lee, Y. Kim, C. Kwak, M.J. Soh, "16bit Multi-energy Level Detecting Photon Counting ROIC", IEEE Nuclear Science Symposium and Medical Imaging Conference Record (NSS/MIC), pp. 801-804, 2012.

- [13] Tanvi Sood, Rajesh Mehra, "Design a Low Power Half-Subtractor Using .90μm CMOS Technology", IOSR Journal of VLSI and Signal Processing, Vol.2, May – Jun 2013, 51-56.

- [14] Martijn F. Snoeij, Albert J.P. Theuwissen, Johan H. Huijsing, and Kofi A.A. Makinwa, "Power and Area Efficient Column-Parallel ADC Architectures for CMOS Image Sensors" IEEE Conference on Sensors, pp. 523-526, 2007.

- [15] Anjali Sharma, Rajesh Mehra, "Area and Power Efficient CMOS Adder Design by Hybridizing PTL and GDI Technique" International Journal of Computer Applications, Vol. 66, No. 4, pp. 15-22, March 2013.

- [16] Pushpa Saini, Rajesh Mehra, "Leakage Power Reduction in CMOS VLSI Circuits", International Journal of Computer Applications, Vol. 55, No. 8, pp.42-48, October 2012.

- [17] Phillip E. Allen Dougles R. Holberg, "CMOS Analog Circuit Design", Oxford University press, pp. 60-667, Second Edition 2002.

- [18] Behzad Rzavi, "Design of Analog CMOS Integrated Circuits" Tata McGraw- Hill, pp. 296, 308, Edition 2002.

- [19] Fang Tang, Denis Guangyin Chen, Bo Wang, and Amine Bermak, "Low-Power CMOS Image Sensor based on Column-Parallel Single-Slope/SAR Quantization Scheme", IEEE Transactions on electron devices, Vol. 60, No. 8, pp. 2561-2566, August 2013.

- [20] Daehee Lee, Minsik Cho, Dong-Uk Kang, Myung Soo Kim, Hyunduk Kim and Gyuseong Cho, "A Complementary Dual-slope ADC with High Frame Rate and Wide Input Range for Fast X-ray Imaging", Journal of the Korean Physical Society, Vol. 64, No. 4,pp. 510-515, February 2014.

International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 7, July 2016

#### **BIOGRAPHIES**

his B.Tech degree in Electronics and Communication Engineering from the Uttar Pradesh Technical University in 2008, currently pursuing his M.E. degree in Electronics and Communication Engineering from Panjab University

(NITTTR, Chandigarh). His current research interests include VLSI Design and Digital Signal Processing.

Dr. Rajesh Mehra Dr. Mehra is currently associated with Electronics and Communication Engineering Department of National Institute of Technical Teachers' Training & Research, Chandigarh, India since 1996. He has earned his Doctor of Philosophy

in Engineering & Technology and Master of Engineering from Panjab University, Chandigarh, India. He has completed his Bachelor of Technology from NIT, Jalandhar, India. Dr. Mehra has 20 years of academic and research experience. He has more than350papers to his credit which are published in refereed International Journals and Conferences. Dr. Mehra has guided 80 ME thesis and he is also guiding 02 PhD scholars. He has also authored one book on PLC & SCADA and developed 06 video films in VLSI area. His research areas are Advanced Digital Signal Processing, VLSI Design, FPGA System Design, Embedded System Design, and Wireless & Mobile Communication. Dr. Mehra is member of IEEE and ISTE.

Deep Sehgal Deep Sehgal is working as Scientist / Engineer in VLSI design in Semi-Conductor Laboratory, Department of Space, Government of India. Graduated from NIT (then REC) Surat, Gujarat in year 1996 in electronics stream; he joined SCL in year 1998. His

dominant field of interest has been in analog design and all these years apart from working at levels of project member to project lead he has peer reviewed many designs and has been involved in testing and debugging of fabricated designs.

H.S. Jatana H.S. Jatana received B.Tech (Hons) from BITS Pilani in 1984 and joined CMC as software engineer, worked on Railway Computerization project for one year. Joined SCL in Oct 84. He has been involved in design of VLSI products, and have contributed in

many design projects like range of transceivers (400Mbps to 1.2 Gbps), power management chips, converters (12-bit pipeline ADC, 12-bit current steering DAC, 16-bit sigmadelta), CMOS Imaging sensor, cold sparing pads, rad-hard tolerant digital cells and memory cell, and many ASICs.

Rockwell Has at Semiconductor for worked design/characterization of R65 series of devices and at Anurag Yadav Anurag yadav received AMS Austria for porting of 2 um and 1.2 um CMOS processes and ATE testing/characterization of products fabricated in these processes. He specializes in analog CMOS design, characterization and ATE testing of VLSI chips.